Why Vitalik Buterin Wants to Change Ethereum EVM on RISC-V

What is EVM?

EVM is a stack-based virtual machine with its own data and instruction model. It is originally designed to execute code on x86, ARM, and other architectures using interpretation or JIT compilation. The main goal of EVM is to ensure the same execution of smart contracts on all nodes of the Ethereum network.

Why RISC-V?

RISC-V is an open command architecture that is not tied to a specific company. It offers flexibility for customization, energy optimization, and the potential to create specialized processors, for example, for blockchain computing. Using RISC-V for EVM provides several advantages:

Open licensing: no licensing restrictions or royalties.

Configuration for specific tasks: you can optimize the processor for specific operations specific to EVM (e.g. high-precision arithmetic, hashing, stack management).

Potential hardware cost reduction: due to the use of an open architecture and simplified design.

Porting challenges and features

Porting EVM to RISC-V is not a simple task. The main challenges include:

1) Execution model: EVM is stack-based, while RISC-V is a register-based architecture. Efficient stack emulation or adaptation to the register-based execution style is required.

2) Memory

optimization: EVM works extensively with memory and data storage, which

requires efficient solutions in RISC-V implementations.

3) Cryptographic

support: Many functions in Ethereum require cryptographic algorithms (e.g.

Keccak-256), which can be implemented either in software or using RISC-V

extensions (e.g. Cryptographic Extensions).

Current Initiatives and Developments

Currently, there are already experiments and projects aimed at implementing EVM on RISC-V:

· EVM-compatible interpreters for RISC-V — creating lightweight interpreters that can run EVM bytecode on RISC-V without a full recompile.

· Native compilers — attempts to directly

translate EVM bytecode into RISC-V machine code to increase performance.

· Hardware accelerators for EVM — projects to

create RISC-V coprocessors that accelerate key operations of smart contracts.

One approach is to create a minimalistic core for RISC-V that executes only the instructions necessary for EVM, which minimizes costs and increases the efficiency of execution in blockchain devices (for example, in validators or crypto wallets).

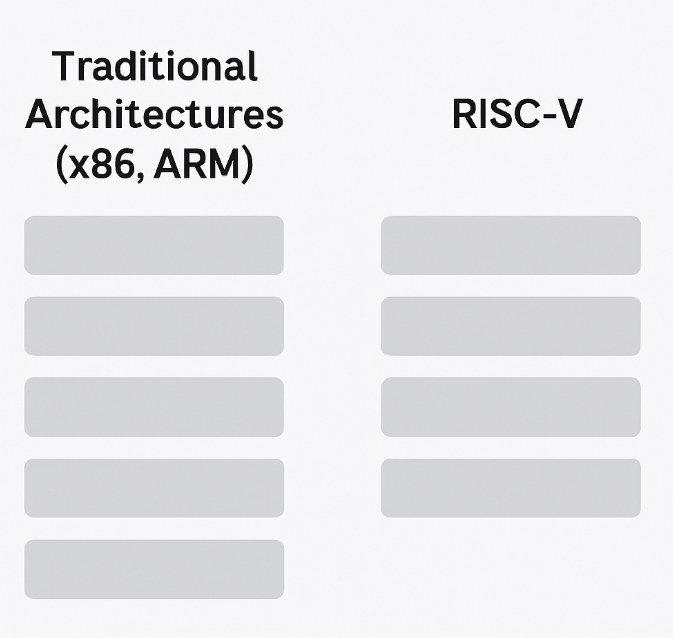

Comparative Table: EVM on Traditional Architectures vs. RISC-V

|

Parameter |

Traditional

Architectures (x86, ARM) |

RISC-V |

|

Licensing |

Proprietary,

often requires licenses |

Open,

free |

|

Optimization

for EVM |

General-purpose,

not specialized |

Possible

targeted optimization |

|

Performance |

High,

but not stack model optimized |

Can be

enhanced with hardware tuning |

|

Cryptographic

support |

Via

libraries and AES/SHA instructions |

Possible

integration of custom crypto extensions |

|

EVM

stack emulation |

Efficient

via high-level abstractions |

Requires

development of optimized model |

|

Development

cost |

Higher

due to licensing and complex ecosystems |

Lower

thanks to openness and modularity |

|

Power

consumption |

Moderate

to high (especially for server-grade) |

Can be

optimized for low power |

|

Flexibility

for blockchain solutions |

Limited |

High

(custom instruction set possible) |

|

Adoption

and maturity |

Very

high |

Growing,

actively developing |

Prospects

The EVM implementation on RISC-V opens up new horizons:

Hardware wallets and validators: cheaper, more secure RISC-V-based devices for working with Ethereum.

Comments ()